TSMC has revealed additional details about its “2nm N2” technology, revealing significant advances in yield and performance metrics.

Introduction of TSMC’s ‘N2 nanosheets’ significantly improves node performance and shows immense potential

The Taiwanese giant’s 2nm process is one of the most anticipated developments in the market. The main reason is that this node is expected to bring a huge leap forward in performance and efficiency results. The process is likely to be mass-produced by the second half of 2025 and is currently being compared with its previous generation counterpart, thanks to the Taiwanese giant’s presentation at the IEEE International Electronic Devices Conference (IEDM) in San Francisco. We have information on the performance of 2nm when , 2nm “nanosheets” were the highlight of the briefing.

TSMC highlights that the 2nm process delivers a 15% increase in performance, up to 30% reduction in power consumption, and significantly improved node efficiency. Additionally, this process increased transistor density by a factor of 1.15 through the use of all-around gate (GAA) nanosheet transistors and N2 NanoFlex. This allows manufacturers to squeeze and optimize different logic cells into the smallest possible area. Node performance.

By moving from traditional FinFET technology to specialized N2 “nanosheets,” TSMC says it will have more control over current flow, allowing manufacturers to fine-tune parameters depending on their process use case. I did. This is possible because the nanosheets feature a stack of thin silicon ribbons surrounded by gates. This ultimately allows for more precise control compared to FinFET implementations.

By adopting such an approach, TSMC’s N2 has provided a slight increase in functionality, especially when compared to 3nm and its derivatives. For this reason, the 2nm process has been improved with each generation and is said to be widely adopted by industry giants such as Apple and NVIDIA. However, with these upgrades, TSMC’s N2 process will also see a parallel increase in wafer prices, making costs more than 10% higher compared to 3nm.

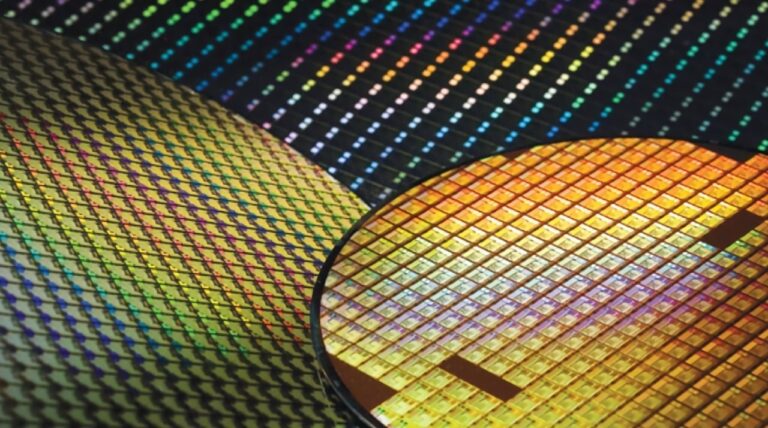

N2 wafers are said to cost around $25,000 to $30,000 per wafer depending on TSMC’s adjustments, but this is a significant increase in price compared to 3nm, which is said to cost around $20,000. Needless to say, initial yield and prototyping considerations will further limit final production, meaning adoption from the process will be slower at the start.